## **AKSHAYA INSTITUTE OF TECHNOLOGY**

Approved by AICTE, New Delhi, Affiliated to VTU, Belgaum, Recognized by Govt. of Karnataka,

Obalapura Post, Lingapura, Koratagere Road, Tumkur - 572 106, Karnataka

#### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

# Module 2 Notes for "VLSI Design and Testing" [BEC602]

**Prepared by:**

Padmavathi N

**Associate Professor**

**Department of ECE.**

**AKSHAYA INSTITUTE OF TECHNOLOGY**

Tumakuru

# **AKSHAYA INSTITUTE OF TECHNOLOGY** Lingapura, Obalapura Post, Koratagere Road, Tumakuru - 572106

## **DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING**

To produce competent engineering professionals in the field of Electronics and Communication Engineering by imparting value based quality technical education to meet the societal needs and to develop socially responsible citizens.

VISION

## **Program Specific Outcomes (PSOs)**

After Successful Completion of Electronics and Communication Engineering Program Students will be able to

- Apply fundamental knowledge of core. Electronics and Communication Engineering in the analysis, design and development of Electronics Systems as well as to interpret and synthesize experimental data leading to valid conclusions.

- Exhibit the skills gathered to analyze, design, develop software applications and hardware products in the field of embedded systems and allied areas.

# MISSION

**M1:** To provide strong fundamentals and technical skills in the field of Electronics and Communication Engineering through effective teaching learning process.

M2: Enhancing employability of the students by providing skills in the fields of VLSI, Embedded systems, Signal processing, etc., through Centre of Excellence.

M3: Encourage the students to participate in cocurricular and extra-curricular activities that creates a spirit of social responsibility and leadership qualities.

### **Program Educational Objectives (PEOs)**

**PEO1:** Graduates exhibit their innovative ideas and management skills to meet the day to day technical challenges.

**PEO2:** Graduates utilize their knowledge and skills for the development of optimal solutions to the problems in the field of Electronics and Communication Engineering..

**PEO3:** Graduates exhibit good interpersonal skills, leadership qualities and adapt themselves for life-long Learning

|                                | VLSI Design and Testing | Semester    | 6       |

|--------------------------------|-------------------------|-------------|---------|

| Course Code                    | BEC602                  | CIE Marks   | 50      |

| Teaching Hours/Week (L:T:P: S) | 4:0:0:0                 | SEE Marks   | 50      |

| Total Hours of Pedagogy        | 50 Hours                | Total Marks | 100     |

| Credits                        | 04                      | Exam Hours  | 3 Hours |

| Examination nature (SEE)       | Theory                  |             |         |

#### **Course objectives:**

- 1. This course deals with analysis and design of digital CMOS integrated circuits.

- 2. The course emphasizes on basic theory of digital circuits, design principles and techniques for digital design blocks implemented in CMOS technology.

- 3. This course will also cover switching characteristics of digital circuits along with delay and power estimation.

- 4. Understanding the CMOS sequential circuits and memory design concepts.

- 5. Explore the knowledge of VLSI Design flow and Testing.

#### **Teaching-Learning Process (General Instructions)**

These are sample Strategies; that teachers can use to accelerate the attainment of the various course outcomes.

1. Lecture method (L) does not mean only traditional lecture method, but different type of teaching methods may be adopted to develop the outcomes.

- 2. Show Video/animation films to explain the different concepts of Digital Signal Processing

- 3. Encourage collaborative (Group) Learning in the class

- 4. Ask at least three HOTS (Higher order Thinking) questions in the class, which promotes critical thinking

5. Adopt Problem Based Learning (PBL), which fosters students' Analytical skills, develop thinking skills such as the ability to evaluate, generalize, and analyse information rather than simply recall it.

6. Topics will be introduced in a multiple representation.

7. Show the different ways to solve the same problem and encourage the students to come up with their own creative ways to solve them.

8. Discuss how every concept can be applied to the real world - and when that's possible, it helps improve the students' understanding.

9. Adopt Flipped class technique by sharing the materials / Sample Videos prior to the class and have discussions on the that topic in the succeeding classes.

**MODULE-1**

**Introduction to CMOS Circuits:** Introduction, MOS Transistors, MOS Transistor switches, CMOS Logic, Alternate Circuit representation, CMOS-nMOS comparison.

[Text 1: 1.1,1.2,1.3,1.4,1.5.1.6.]

Teaching-Learning Process: Chalk and talk method, YouTube videos, Power point presentation RBT Level: L1, L2

**MODULE-2**

**MOS Transistor Theory:** n-MOS enhancement transistor, p-MOS transistor, Threshold Voltage, Threshold voltage adjustment, Body effect, MOS device design equations, V-I characteristics, CMOS inverter DC characteristics, Influence of  $\beta n / \beta p$  ratio on transfer characteristics, Noise margin, Alternate CMOS inverters. Transmission gate DC characteristics. Latch-up in CMOS. [Text 1: 2.1,2.2,2.3,2.4,2.5.2.6.]

#### MODULE-3

CMOS Process Technology: Silicon Semiconductor Technology, CMOS Technologies, Layout Design Rules. [Text 1: 3.1,3.2,3.3.]

Circuit Characterization and Performance Estimation: Introduction, Resistance Estimation, Capacitance Estimation, Switching Characteristics, CMOS gate transistor sizing, Determination of conductor size, Power consumption, Charge sharing, Scaling of MOS transistor sizing, Yield. [Text 1: 4.1,4.2,4.3,4.4,4.5.4.6,4.7,4.8,4.9,4.10]

#### **Teaching-Learning Process:**

Chalk and talk method/Power point presentation, YouTube Videos RBT Level: L1, L2, L3.

#### **MODULE-4**

CMOS Circuit and Logic Design: Introduction, CMOS Logic structures, CMOS Complementary logic, Pseudo n-MOS logic, Dynamic CMOS logic, Clocked CMOS Logic, Cascade Voltage Switch logic, Pass transistor Logic, Electrical and Physical design of Logic gates, The inverter, NAND and NOR gates, Body effect, Physical Layout of Logic gates, Input output Pads. [Text 1: 5.1,5.2,5.2.1, , 5.2.2, 5.2.3, 5.2.4, 5.2.6, 5.2.8, 5.3,5.3.1,5.3.2, 5.3.4, 5.3.8,5.5]

**Teaching-Learning Process:**

Chalk and talk method, YouTube videos, Power point presentation RBT Level: L1, L2, L3.

#### MODULE-5

Sequential MOS Logic Circuits: Introduction, Behaviour of Bistable Elements (Excluding Mathematical analysis) SR Latch Circuit, Clocked Latch and Flip-Flop Circuits, Clocked SR Latch, Clocked JK Latch.[Text2: 8.1, 8.2, 8.3, 8.4]

Structured Design and Testing: Introduction, Design Styles, Testing[Text1: 6.1, 6.2. 6.5]

#### **Teaching-Learning Process:**

Chalk and talk method/Power point presentation RBT Level: L1, L2, L3

#### **Text Books:**

- 1. Principals of CMOS VLSI Design A System approach Neil H E Weste and Kamran Eshraghain . Addition Wisley Publishing company.

- 2. "CMOS Digital Integrated Circuits: Analysis and Design", Sung Mo Kang & Yosuf Leblebici, Third Edition, Tata McGraw-Hill.

#### **Reference Books:**

- 1. "CMOS VLSI Design- A Circuits and Systems Perspective", Neil H E Weste, and David Money Harris 4th Edition, Pearson Education.

- 2. "Basic VLSI Design", Douglas A Pucknell, Kamran Eshraghian, 3rd Edition, Prentice Hall of India publication, 2005

| Cou        | Course Outcomes: After completing the course, the students will be able to                                                |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| CO1        | Apply the fundamentals of semiconductor physics in MOS transistors and analyze the geometrical effects of MOS transistors |  |  |

| CO2        | Design and realize combinational, sequential digital circuits and memory cells in CMOS                                    |  |  |

|            | logic.                                                                                                                    |  |  |

| CO3        | Analyze the synchronous timing metrics for sequential designs and structured design basics.                               |  |  |

| <b>CO4</b> | Understand designing digital blocks with design constraints such as propagation delay                                     |  |  |

|            | and dynamic power dissipation.                                                                                            |  |  |

| C05        | Understand the concepts of Sequential circuits design and VLSI testing                                                    |  |  |

Generations of Ics :-

| Year | Generation | No of O          | Examples                  |

|------|------------|------------------|---------------------------|

| 1961 | SSI        | 10-100           | Logic Galer, FF, Coortens |

| 1966 | msī        | 100-1000         | Adden, mux, countern.     |

| 1971 | LSZ        | 00006-000        | Shit Mpr, RAM. Rom        |

| 1980 | VLSZ       | 20000 - 1million | 16 & 32 bit leps, DRA     |

| 1990 | VILST      | 1-10 million     | DSP1, Smerit Senson.      |

| 2000 | GSE        | > 10 msllion     | Asica, Soc                |

Moore's law: (Gordon moore, 1965) "The number of transiston, integrated on IC doubles for every 18 months".

Truly the 19 ton, 801, 901 may be regarded on Integrated wrows era.

Mos Transvistors: (metal orade Semiconductor) mos structures are evealed by Superimposition sweral layen of conducting and insulating ( sweral layen of conducting and insulating ( materials to tom a Sandwich like Structure. materials to tom a Sandwich like Structure. cmos technology poourdes two types of transister an n-type and P-type transister. Transister operation is based on electric fields hence they are called as field effect stransister.

cross section and symboly of these On (2) are shown The not and pt region indicate heavily doped nor p-type Silicon. obrain spolyselicon Source of Gate D-rain Source Gale - Sio2 <nt nt bulk S: balk si P Substrate or bulk pmos Transistormmos transistor An mmos transistor is built with a ptype body and has region of an type seniconductor adjocculto gate called the source and drewn. They are physically equivalent and interchangeable. The body is typically frounded. A ponos transistor in just opposite, conteurs p type Source and drain region weith to type body. For a nomes transistor when g=0, p-n gunchions of the Same and drain to beely are reverse brased and transistor is OFF. When g=1 transistor in one.

electron say majority ca

To study the behavior of mos transistor (3) Consider a mos structure with gate and body but no source or drain. Fig show Simple mos Structure. The top layer is good conductor called a gate made up of polysolicion. The middle layer is this insulating delin of Silos called gale oxide. The bottom layer is the doped Silicon body (p) The body in grounded and voltage in applied to gate Depletion Invertion re DOOD Gale DO 0000 Ug20 CEREDECT DE 0000000 • • • • • • P type bady 6666666 vg>vt oradraf VgCO (b) Depletron (c) Sincersion (a) accumulation

To dig cas, we voltage is applied to the gale so there is negative charge on the gale. The free holes are altracted by we vig on gale and gets collected under the gate. Thus in called incommutation mode. So fig is low the vig on gate, repets the hole, and resulting in a depletion region doming below the gate. In stigics higher the potential is applied togale.

such that vg>vt. The holes are repelled. durther and small number of free electrons in the body are altracted to the region beneat the gate. This conductive layer of electron in the p-type body is called the invertion layer The threshold vig ve dependen on owner of dopants in the body and thickness ton of the oxide. mas tranistos operation:-VGS=0 J g J Vgd vgs>ut ] g \_ ugs = ugs JODEE DE DE VIEO p-type Body Ptype Body a) cutent : No channel (5) Linear, channel formed Eq. Eds = 0 Ids Mereaser with vds ndisht 13-1 nagent 3 + yg, >vga >v4 Vgs>Vt 11) & Sels 1S L DE OBO DOE ODO 1 IIds OCOOP OCUS Vg-Vt 00000000000000 P type Body Ptype Body Vaszvge-Vb Saturation: channel pitched eff Linear

Scanned with CamScanner

To dog car, vgs < vt. The Source and dram ? have free electron. The body has free holes but not free electrons. The junction between the body and source or drawn are reverse bracked so no current flows. Thus mode of operation is called cutoff.

hed

3

In tig(b) Ugs>VE. Now the inversion region of electron called the channel connects source and drawn, creating conducting path. The conducti -vity in the channel depends on gate voltage. The potential defference between drain and source is Vds = vgs-vgd. when vds = 0 ie vgs = vgd, no current thous from drean to source. In fog (c), a small positive pokatial in applied to drawn, therefore current Ids flower through channel from draw to source. Thus made 21 Operation M Called linear, resistive, non saturated or unsaturated. This Current Eds moreaser with drewn vig and gate vig States (d), vds in sufficeeotly large such that ugd > 4 the channel is no loger inverted onear the drawn and becomes pinched off. Now Ids becomes independ nt 9 vas and controlled by only gateviz. This mode is called saturation

Summary 9 nmos D vgs <vi - entoff Ids = 0 vgs >vt, vds &mall -> linear region -> Eds flow. vgs > vt & vds is large -> acts as current Source -> Ids becamer independent g upe The prostransistor operates in just the oppossife may. Source 16afe, prais pf P+ n-type Body I deal I-V characteristien : Elong channel Ev cham In linear and Salvration region, the gate altractus carroeni to form a channel. The carmen dreft- toon source to drawn out-c vate proportional to electric field blus sand D. mos structurer looks loke rel plate capacitor. where operating in inversion. we can and currents of we know the amount of charge in the channel and rate al which it moves

· we know that D= cv. (5) Thus the charge in the channel is Reharmel = Cg (Vgc - Vt) where g -> Gale to channel capacitance Vgc-Vt -> Ng attracting charge to channel to invert- from p to or. Vgs = vgd pD channel vd 1 Avd. 7 Sto 2. Ptype Body Aug Gale to channel potential Transistor dimension. If the source is at is and drawn is at VD, then the average in Ve = (VS+Vd) : The mean diff blue gave & channel 2 [: 2VS+VdS = 2VS+Vd-VS 2 2 potential is, 'ugc=(Ugs+ugd) = Ugs-Uds = VS+Vd ] If the gale has length L and weighth as and the onude thickness is ton as shown the Capacitance is Cg = Eon WL , Where Eon = 3.9EO for Sion and Eo is Ite permitivity 9 free Space, 8.85×1514 Flum.

Summary

Summary

$$\int_{a}^{b} \sqrt{9} \sqrt{1}$$

wholf

$\int_{a}^{b} \sqrt{9} \sqrt{1}$  wholf

$\int_{a}^{b} \sqrt{9} \sqrt{1}$  whose  $\sqrt{10}$  whose  $\sqrt{10}$  whose  $\sqrt{10}$  whose  $\sqrt{10}$  where  $\sqrt{10}$  w

n. 0

. .

De Transfer characteristics -\* The De transfer characteristics relate the output- vig to the mput college, assuming that input voltage Changes slocoly So that internal capacitance can change or discharge fully. Consider a complementary cmos inverter a shown -VDD pmos JAIdosp Vow-De transfer function is plot blue Voul and Vin Relations between voltages too the 3 region of operation Saturation linear whoff vgsn >Utn Ugso>Vtn vgsn<vtn Vin >Vtn Vin >Vtn vin «vtn nmos Vdsn > Vgsn-Vtn Volsn & vgsn - Vtn Vout > Vin-Vin Vow Vin - Vtn Vgsp < Vtp Vgsp < Vtp Ngsp 2nth VIN < Vtp+VAD Visi < Vtp + VDD Vin >Vtp+VDD Vdsp < Vgsp - Utp Vdap >vgsp -utp ponos Vow - XVin - Vtp Vow >Vin -Vtp Vitn > Threshold voltage too mos VtR -> Threshold Voltage for pros

Vtp is viegative.

By the Source of omos transistor is grounded,

Ugsn = Vin and Vdsn = Vout.

By the Source of pmos transistor is connected to

VDD, Vgsp = Vin-VDD and Vdsp = Voud - VDD.

To divid the transfer Chay (Vout vs Vin),

assume,

Idsn = Ifdsp)

Vtp = -Vtr)

Bn = Bp

The Important equation for mos transistors are

Sos = B(ugs - ut - vds) Vds

S IDS =

$$\frac{B}{2}$$

(Vas - Vt)<sup>2</sup>

S IDS =  $\frac{B}{2}$  (Vas - Vt)<sup>2</sup>

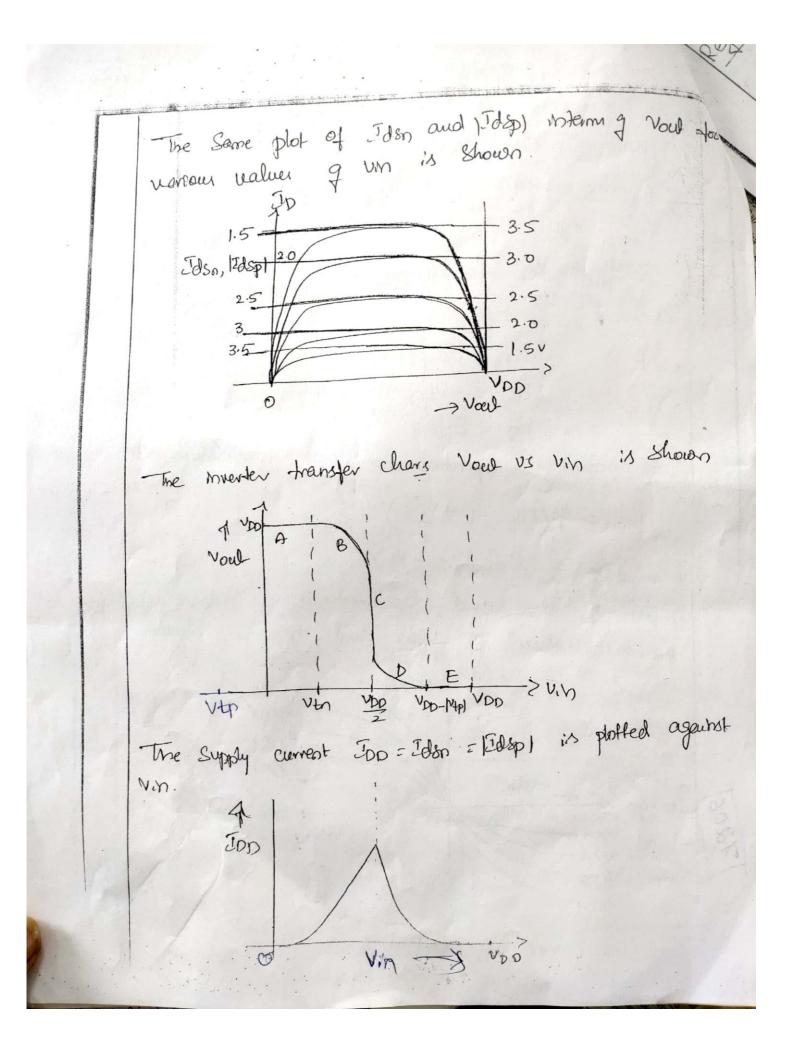

B jot of Idsn and Jdsp interms of Vdsn & Vdsp ofor

Vareous value of Ugsn and Ugsp is Sheero.

$\frac{1}{2} \frac{2}{2} \frac{1}{2} \frac$

Perfor A The region is defined by

$$0 \le \forall v_1 \le \forall \bot_1$$

where Nmos- where and pmos- linear.

The olp vills in Vocil = Vod

given B: Thus region is defined by  $\forall t_1 \le \forall v_1 \le \forall v_2)$

where pmos- linear ( $\forall d_5 \pm 0$ ), Nmos-  $saln$  region

The equivalent dat in given by,

$T_{34sq} = v_{out}$ .

These is obtained by  $\forall g = 4v_1$  For N Denvice

$v_{3s} = \sqrt{1}$

Tass is obtained by  $\forall g = 4v_1$  For N Denvice

$v_{3s} = \sqrt{1}$

$T_{3sq} = v_{out} - v_{tr}$

$V_{0s} = \sqrt{1}$

$T_{0s} = \beta_0 \frac{(v_{10} - v_{tr})^2}{2}$   $v_{0s} = \sqrt{10}$

$v_{0s} = v_{0u}$

$whore  $\beta_{01} := den \beta_{01} \left[ \frac{v_{02}}{t_{10}} \right]$

$whore  $\beta_{01} := den \beta_{01} \left[ \frac{v_{02}}{t_{10}} \right]$

$whore  $\beta_{11} := den \beta_{01} \left[ \frac{v_{02}}{t_{10}} \right]$

$whore  $V_{0s} = V_{00} - v_{00}$

$v_{ds} = V_{0ut} - v_{00}$

$v_{ds} = V_{0ut} - v_{00}$

$T_{0s} = p \left[ (v_3 - v_1) v_{0s} - v_{0s} \right]$   $v_{01} = 1 \int_{0}^{1} s_{0s}$

$T_{0s} p = p \left[ (v_{10} - v_{10}) - v_{10} \right] (v_{00} - v_{00})$

$- \left( \frac{v_{cut} - v_{00}}{2} \right)^2$

$u_{01} = \frac{1}{2} \int_{0}^{1} s_{01} \int_{0}^{1} s_{01}$

$u_{01} = \frac{1}{2} \int_{0}^{1} s_{01} \int_{0}^{1} s_{0$$$$$

$$\begin{aligned} \begin{bmatrix} U & KT \\ Jdsp &= -Idsn \\ Jdsp &= -Idsn \\ F & C(h - V_{00}) - V_{0p}(V_{add} - V_{00}) - (V_{00d} - V_{00})^2 &= F_{0} F_{0} F_{0} - V_{12} J^2 \\ Solving we gd. \\ V_{add} &= (V_{10} - V_{1p}) + (U_{11}/V_{1p})^2 - f_{pp} - (V_{11} - V_{1n})^2 \\ -g V_{0D}(V_{11} - \frac{V_{00}}{2} - V_{1p})^2 \\ V_{ad} &= (V_{10} - V_{1p})^2 - F_{0} (U_{11} - \frac{V_{00}}{2} - V_{1p})^2 \\ V_{ad} &= (V_{10} - V_{1p})^2 + (U_{11}/V_{1p})^2 - g(V_{11} - \frac{V_{00}}{2} - V_{1p})^2 \\ V_{ad} &= (V_{10} - V_{1p})^2 + (U_{11}/V_{1p})^2 - g(V_{11} - \frac{V_{00}}{2} - V_{1p})^2 \\ V_{ad} &= (V_{10} - V_{1p})^2 + (V_{10} - V_{1p})^2 - g(V_{11} - V_{00} - V_{1p})^2 \\ V_{ad} &= (V_{10} - V_{1p})^2 + (V_{10} - V_{1p})^2 - g(V_{10} - V_{1p})^2 \\ Jdsp &= -F_{0} (V_{10} - V_{10}) - V_{1p})^2 \\ Jdsp &= -F_{0} (V_{10} - V_{10}) - V_{1p})^2 \\ Jdsp &= -F_{0} (V_{10} - V_{10}) - V_{1p})^2 \\ Jdsp &= -Idsn \\ on Substituting and Simplifyzed, we go. \\ V_{11} &= V_{00} + V_{11} + V_{11} + F_{0} \\ F_{11} &= F_{11} \\ F_{11} &= V_{11} \\ F_{11$$

Region D: Here Vin > Vooj and Vin < VOO + Vtp p device is in Sath and or device is in linear region as shown Idsp = - Pp (Vin - Vap - Vtp)2 Jos 1 Devous Idon = Bn [(Vin-Vtn) Vour - Vour ] Idon \$ Idan = - Idap wegel. Vau = (Vin - Vtn) - ((Vin - Vtn)2 - Bp (Vin - VDD - Vtp)2 Region E: - Hore Vin > Voo + Vtp. p dervee is in cutoff and a dervee is in linear region : Vous = 0 Simmary q cmos inverter operation: oupul-N' Denice PDeurge condition Region Voul = VUD Linear intoff 05 Vin 5 Vtn A Vow > Von Saturated Linear Vtn < un < VDD vous drops salvrated B Saturated Vin = VDD Voul < Vop C Linear Saturated VDD < Vin < VDD-1/4 Voul = 0 D Linear curoff Vin > VOD - VIDI E

Scanned with CamScanner

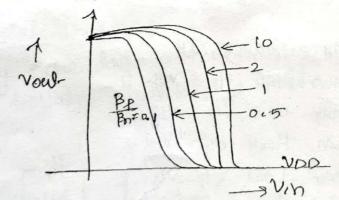

Beta Ratio Effects :-Inverten with different beta ration BP/Bn are called skewed inverten. of PP/Bn >1, He inverter is HIZ- skewed. If Bp<1, He inverters is 20-Skewed If BP =1, the inverter is normal or Unskewed High Skew invertere has stronger pros transistor and require higher threshold. LO-Skew inverten has wear pros and then I be Switching threshold. Fig below show Skewing impact on DC -Iramster char As beta ratio is changed, use Swotching threshold moves but the output vig transition renain sharp.

NOTE: When temp is raised, mobility (u) decrease : \$P/po vatio decrease, and curves shifts to reft.

Moise margin :- Noise -margin or moise immunity in allowable input gale voltage so that output we not be corrupted. Two parameters are used to Speufy noise margen, Low noise margen rem and HIGH moise margin NMH. NML is defined as the defference in maximum Low input voltage recognized by the receiving gale and the manimum Low output vig produced by the driving gate. NIML = VIL - VOL NMH in defined as the difference between the minimum that old vig of driving gale and the minnum that input up recognized by the recercing gode - Thuy, NMH = VOH - VIH where VIH -> min HIGH Mp VIZ VIL - s max Low ilp Vlg Volt -> min High olp Vig VOL- Mar Low olp Vig. Moire margen définition are shown below. olp chor ip char HIGH VIH 41611 TIMH Volt Forbidden VIL VOL NIN LOW Low

The voltage levels on transfer char are shown in the VOD unoty gain points Voti Slope =-1 Voul VOL VIL VIH. VDD It is desirable to have VIH and VIL Should be close to each other re to sueville transfer charge abruptly. Typical values of & noise margins one NML = 0.46 VDD NMH = 0.34 VDD when input is all worst legal value, the olp is slightly degraded, called as nois feed through or propagaled noise

## Mon Ideal IV effects :-

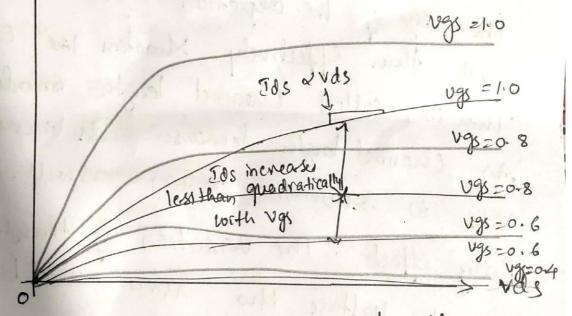

The long channel & model negledu many effects that are important to devices with channel lengths below 1 micron.

Fig below Shows i deal IV characteristics and Simulated IV characteristics of a 1-41 wide mos transistor in 65 nm process.

Jds1

The Saturation current increases less than quadratically with increasing ugs. This is due to two effects: velocity saturation & mobility degradation.

Ve locity <u>Saturation</u>: At high lateral dield Strengtha (vds/L), Carrier velously ceases to increase Whearly with doeld Strength. This is called

Eds than expected at high Vds. mobility degradation: At high vertical dield Strengthn (vgs/tox), the constean Scatter off the oxide interface more offen, Slowing their progress. This results in ten current (Sel) than expected at high ugr. channel length modulation: - Higher VDS increases Ibe size of the depletion region around the draw and thus effectively shooten the channel. Thuis called channel length modulation. As channel length decreases Eds increases with Vols in Saturation region as well. Body effect. The variation of threshold voltage due to Voltage blu Sarre and body (VSb) is called body effect. subthreshold effect conduction: For ugs<VI. He current about off exponentially rather than abruptly becoming zero. Thus in called sub the -exhalt conduction. Junction leakage: The reverse bigsed divides across Jos conduct small amont of current to called in leakage.

obecs (e WT-i) Trennelling: The current in to gate it ideally O. However as the thickness of gate Oxide reduces to only small number of atomic layer, election termes through the gate, causing some gate current. It is called termeling. Temp dependance. Tremistar characteristic eine influenceed by temp. Cornier mobility decreases Noots temp. The relation in green by,  $\mathcal{U}(T) = \mathcal{U}(T_r)(T) = (T)$ T- absolute temp Tr - room temp Ku-fitting parameter (1.2-2.0) mobiloty Degradation and velowity Serturation: The long channel model assumed that carrier mobility is independent of applied dields. Thus assumption in good for low dields but not for Stronger foelds. The carroen attain manimum Velouty Vsar when high fields are applied. Thus is called velocity saturation.

Fig shall carrier velocity vis election Jup holes electric feeld & blow DES. Al low drelds, velowity increases linearly with doeld. The Slope is reft. At fields above a evolveal E level Ec, the velocity bench and at usal  $v = \int \frac{def E}{1 + E}$ ELEC Vsal E >/EC where Ec = 2 Vsal Note yelouty Saturation refers to the limiting of Carrier velocity at high field. ] problem. Find the initical vig to fully on mmos and pmos transistom using the effective mobilities

channel leight Madulation:

As Vds increases, depletion region around drain

region increases with a width by as shown

if it is a star

ptype body

It depletion region effectively shortens the

channel length to

Left = L - Ld

As Vds increases, channel length decreases and

results in higher current, thun Eds increases

worth Vds in saturation.

Eds =

$$\frac{B}{2}(V_6 - V_1)^2 [1 + Vds]_{V_A}]$$

where VA-> Early Voltage.

VA:s propositional to channel length.

Threshold voltage Effects :-So far, we have treated threshold vig as a constant. However ut increaser with the Source ulg, decreases with body vig, decreases with draw viz and inenearses with channel length. O Body Effect- : Body in the another implicit fourth terminal for a mosfer. When usb is applied between the source and; body, it increases the amount of charge required to invert live channel, here it increases live v6. The threshold vig can be modeled as, Vt = Vto + 2 (Jos + Vsb - V os) where Vto 2> threshold Vig bohen s in at body potential Qi -> Surface potential at threshold → body effect coefficient (0.4 to 1 v 1/2) Ps= 2VT In NA 7 = tox 12925; NA = 12925; NA

Dreun induced Barrier Lowening: The drain viz vas creater an electric field that affects like threshold viz. This drews induced barrier lowening (DJBL) effect- is important in Short channel transistory. It can be modelled as Vt = Vto -n Vds where of is the DIBL coefficient DIBL "Eaurer Eds to increase with uds in sate 3 short channel Effect : The threshold voltage typecally increases welts channel length. This phenomenon is important for small L where s and D depletion region extend into channel region. Leakage: when the transiston are normally DFF, they beak small amounts of current. Different types à leakage currester include subthreshold Conduction blue s and D, gate leakage from G junction leakage from S to body to body and and drawn to body, an shown. 7 Igate 29 00 Leakage current paths , Body

Subthreshold conduction is Caused by thermal emission of connection we patential become set by the threshold. Gate leakage is quartum mechanical effect. Caused by tunneling through the extremely this gate dielectric. Junction leakage: is caused by current through be pn in blue the slo diffusions and the body